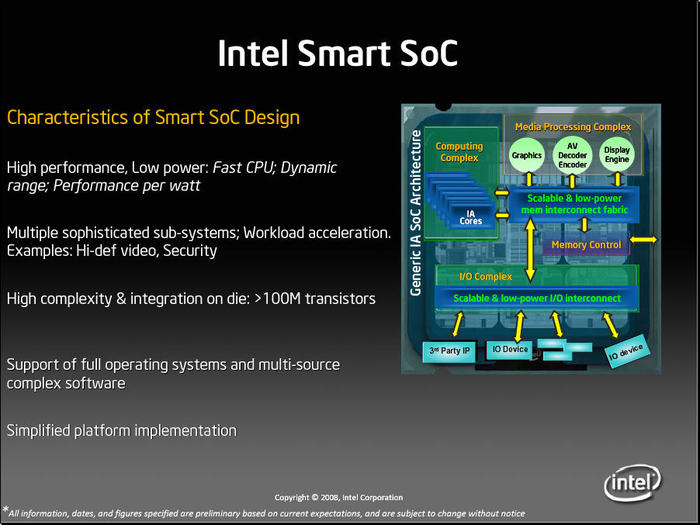

图:多核片上系统有望极大提升复杂图形,多媒体等处理性能

近五年以来,Intel、IBM等国际一流公司开始发布大量基于片上网络 (network-on-chip,NoC)的多核片上系统,片上网络是片上系统 (system-on-chip,SoC)的一种新的通信方法。它是多核技术的主要组成部分。片上网络方法带来了一种全新的片上通信方法,显著优于传统总线式系统的性能。基于片上网络的系统能更好地适应在未来复杂多核片上系统设计中使用的全局异步局部同步的时钟机制。

片上网络作为一种片上多核系统核间互连方案开始进入实用化阶段。

图:Intel的智能片上系统

随着片上网络性能、功耗等诸多问题逐步被解决,可靠性问题已成为阻碍片上网络进一步发展的主要问题。

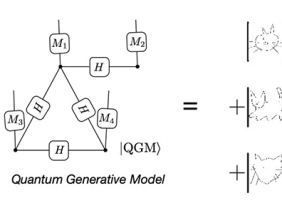

近日,电子科技大学低功耗集成电路与系统研究所黄乐天老师在计算机体系结构领域顶级期刊《IEEE Transactions on Computers》发表题为“Non-Blocking Testing for Network on Chip”(面向片上网络的非阻塞式测试方法)的研究论文。

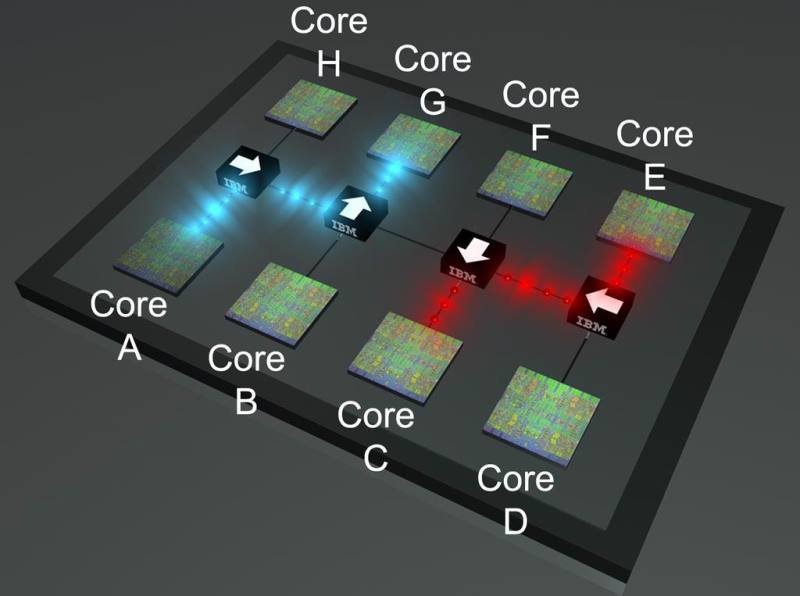

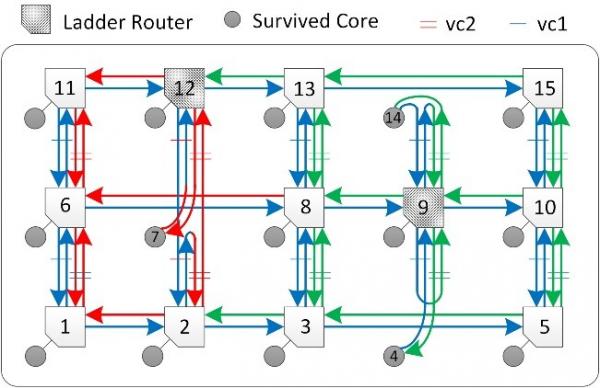

此次发表的论文通过设计一种可重构的片上网络路由器和自适应路由协议,构造了一种在部分片上路由器处于测试状态时依然可以维持系统全连通的片上网络。论文所提出的设计方案可以在多核片上系统正常工作状态下及时发现并定位出片上网络中隐藏的缺陷,并使系统在发生重大问题前能被及时地保护和修复,对提升片上网络甚至整个片上系统的可靠性具有重要价值。该文章被作为当期的首篇论文发表,并入选当月最受关注的50篇论文。(参见:仿真器演示视频)

图:论文中提出的自适应可重构片上网络架构

低功耗集成电路与系统研究所简介:

低功耗集成电路与系统研究所成立于2016年,是我校创新领域平台建设的首批两个校级研究所之一,由微固学院李强教授负责,是我校面向集成电路主流的低功耗研究方向,以及摩尔定律走向饱和、集成电路向集成微系统演进的趋势而建立的跨学科平台。研究所以“纵向集成”为主要思路,以低功耗集成电路设计为中心,着力探索从器件、电路、体系结构到系统的集成设计技术,力争为我校建立一个优势突出、特点鲜明的研究高地。

论文链接:

Letian Huang, et al, "Non-Blocking Testing for Network-on-Chip," IEEE Transactions on Computers, 65(3), 2016

下载链接:ESY系列仿真器开源软件

黄乐天老师简介:

电子科技大学信息与通信工程学院讲师,Email:huanglt@uestc.edu.cn

个人主页:点击此处进入

研究方向:以通信信号处理算法、架构及实现,片上系统与片上网络,高能效并行计算系统,混合信号集成电路设计等。

(本文信息来源:电子科技大学网站;)

如若转载,请注明e科网。

如果你有好文章想发表or科研成果想展示推广,可以联系我们或免费注册拥有自己的主页

- 片上网络

我要投稿

我要投稿